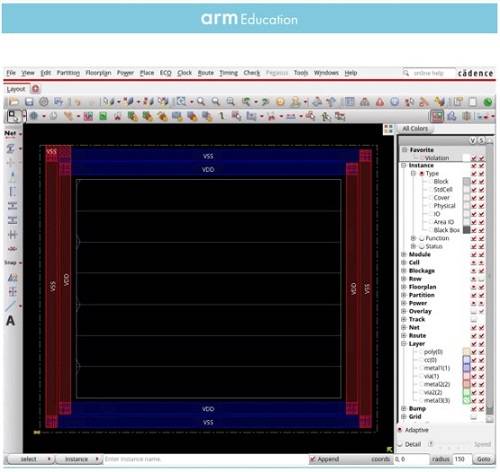

▲사진=케이던스

반도체설계자동화(EDA) 툴 업체인 케이던스는 영국 반도체 설계 IP회사인 Arm의 ‘VLSI 기초과정–실습 교육키트’에 케이던스의 최신 디지털 임플리멘테이션 소프트웨어를 활용해 교육키트를 최적화할 수 있도록 지원한다고 2일 밝혔다.

이에 따라 학생들은 VLSI 교육키트를 통해 전기장 효과, 채널길이 변조, 문턱 전압 효과 및 누출로 인한 비이상적 트랜지스터의 특성, 잡음, 직류(DC) 응답 및 RC 지연 모델을 포함한 CMOS 회로의 특성 추정 방법을 배울 수 있다. 온칩(on-chip) 와이어의 저항, 정전 용량 추정, 온칩 와이어에서 와이어 지연, 전력소비 및 혼선 최적화 방법 등에 대해서도 학습할 수 있다.

이외에도 칩 설계에서 다양한 지식을 습득할 수 있어 VLSI에 대한 이해를 심화시킬 수 있다는 특징을 갖고 있다. 예를 들어, 테스트의 중요성과 고장 고착, 자동 테스트 패턴 생성(Automatic Test Pattern Generation), 내장된 자체 테스트 기능(Built in Self-Test), 다른 SRAM 아키텍처, 회로의 전원 소산원, 전력손실 제어, 온칩 변동의 원인 및 효과, DC 전송 특성 등 심화학습이 가능하다.

아울러 학생들은 VLSI 교육키트를 통해 케이던스의 최신 디지털 임플리멘테이션 소프트웨어인 ‘지너스 합성 솔루션’을 이용해 하드웨어 언어에서 로직 게이트를 합성한다. 또한 ‘이노버스 임플리멘테이션 시스템’을 사용해 로직게이트설계 배치 및 라우팅, 회로설계도, 레이아웃을 이용하여 칩을 설계하고, 패드 프레임을 추가한 다음 케이던스 버츄오소 디지털 임플리멘테이션을 이용해서 테이프-아웃(tape out)용 GDSII 포맷으로 추출, 다양한 실습을 할 수 있다.

한편 VLSI 교육키트는 Arm의 유니버시티 프로그램인 AUP에서 작년에 발표한 실습 교육키트다. 20개의 모듈이 포함돼 있고, 강의 슬라이드 및 실습으로 구성돼 10-12주짜리 일반 학부 과정에 적용할 수 있다. VLSI 교육키트는 케이던스 아카데미 키트에서 내놓은 첫 결과물로, VLSI 키트의 추가적인 업데이트뿐만 아니라 앞으로도 다양한 교육키트 제작으로 교수 및 학생의 학습을 도울 예정이다.

VLSI 교육키트는 케이던스 아카데미 네트워크 웹사이트에서 등록한 후 ‘VLSI 기초과정- 실습 교육키트’를 다운로드 가능하다.

이윤혜 기자 dbspvpt@datanews.co.kr

[ⓒ데이터저널리즘의 중심 데이터뉴스 - 무단전재 & 재배포 금지]

많이 본 뉴스